芯片制造-硅工艺

半导体

半导体分为无机半导体和有机半导体,无机半导体又分为元素半导体、化合物半导体、氧化物半导体。元素半导体,顾名思义,是由单一元素形成的半导体,例如硅、锗、碳等,当前最常用的是硅

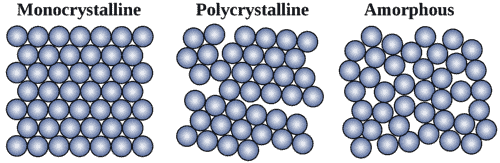

固态硅三种形态

硅原子与周围 4 个硅原子以共价键结合形成规则排列的结构,称为单晶硅(Monocrystalline Silicon);多晶硅(Polycrystalline Silicon)是由许多称为晶粒的单晶硅小颗粒任意聚集形成的集合体,晶粒间相连接的部分称为晶界;非晶硅(Amorphous Silicon)是整个结构中都没有规律性状态的硅,又称为无定形硅或非晶质硅。单晶硅、多晶硅与非晶硅在被制作晶体管等电子元件时,电子速度依次变慢,漏电流依次变多

芯片制造过程有个退火过程,通过退火处理,可以使结晶体内部重新排列,去除大部分缺陷和杂质,恢复晶格完整,提高晶体电导率和电学性能。退火前的工艺不能使用熔点低于退火温度(800 度以上)的金属,例如铝。如果使用铝作为栅极材料,则 MOS 管的栅极和源漏不能在一次曝光工艺完成,而多次曝光会造成栅位置偏差,影响器件参数与性能。多晶硅的熔点高于退火工艺,且多晶硅在不同渗杂工艺下可以改变其电特性,为了实现**自对准栅工艺**,多晶硅成为了 MOS 管栅极材料

渗杂与能带

作为不含杂质的本征半导体,“单晶硅” 中电子的能量处于被称为导带及价带的能量区域,这两个能带之间电子不能存在的能量区域被称为禁带。硅的禁带宽度是1.1eV(电子伏特)。作为本征半导体的单晶硅,在室温条件下,价带被束缚电子填满,而由于导带中几乎没有电子,因此不存在能够自由移动的电子。此时单晶硅的电阻率很大,基本上没有电流通过

单晶硅处于室温时由于掺杂产生的具有一定能级的电子很容易向导带上迁移,成为自由电子。单晶硅中加入微量 Ⅴ 族导电型杂质磷(P)、 砷(As)时,导带下面的禁带中出现了通过掺杂产生的可以存在电子的位置(能级)。 这个能级在导带的下方,对于磷是在导带下方 44meV 处。单晶硅中加人微量 Ⅲ 族导电型杂质硼(B)时,价带上方的禁带中出现了由于掺杂硼而产生的能够存在电子的能级,这个能级在价带上方 45meV 处

构成电路的元器件大概可以分为无源元件和有源器件。无源元件不具备放大信号的功能,只能消耗和储存电能,比如电阻 、电感、电容都是无源元件。半导体上电阻分扩散型、多晶硅型;电容有 PN 结、MOS 型;

- \(n^+\) 和 \(p^+\) 扩散区和漏区是指重渗杂的 n/p 型硅

- 金属与轻掺杂半导体之间的结形成了只能沿一个方向传送电流的肖特基二极管,当半导体掺杂较重时,它与金属间形成良好的欧姆接触,因而对双向电流都呈现低阻

- PMOS 管往往比 NMOS 管宽,因为空穴比电子移动得慢,因而 PMOS 管必须宽些才能传送相同的电流

半导体工艺

平面 MOSFETs

MOSFETs(Metal Oxide Semiconductor Field Effect Transistors) 集成电路主要由几种不同的材料组成:单晶硅衬底渗杂构建 p/n 沟道晶体管 / 二氧化硅绝缘层 / 多晶硅(Ploy),晶体管栅极、互联材料 / 铜/铝,金属互联材料 / 其他,例如五价、三价渗杂

对于典型的 0.35um 工艺,多晶硅层的片电阻是 \(10\ \Omega/\square\),而扩散层的片电阻大约为 \(3\ \Omega/\square\),铝的片电阻则是 \(0.06\ \Omega/\square\)。 因此,多晶硅层应谨慎使用,大多数布线则采用金属层。多金属层的布线需要通孔(Via),对于同样的 0.35um 工艺,两个金属层之间 Via 的电阻一般是 6Ω,而接触层的电阻则显著更髙,是 20Ω。接触层一般用于金属层和多晶硅或器件之间的连接,通孔用于连接不同的金属层

在典型的 65nm 工艺中,多晶硅层的片电阻是 \(12\ \Omega/\square\),而扩散层的片电阻是 \(17\ \Omega/\square\),铜金属层的片电阻相比于 0.35um 制程下的铝,因为更薄所以更大,是 \(0.16\ \Omega/\square\)。通孔和接触层分别是 1.5Ω 和 22Ω

半导体 IC 的制造过程(2011年前后),大致可分为前工序和后工序两个过程。所谓前工序,是将晶体管等原件以及连接它们的内部配线镶嵌到硅片上。前工序又称为扩散工序,由上百步的步骤组成,占整个工程的 80% 左右。前工序又可分为 FEOL (front end of line) 和 BEOL (back end of line) 两个过程,其中 FEOL 是将晶体管等原件嵌入到硅片上的工序,而 BEOL 是将原件间的配线(包括多层配线)连接起来的工序

后工序分为组装工序以及检查筛选工序。组装工序是将检测完电气特性的晶片分成一个个的集成片封装成器件的工序。检查筛选工序是对封装到器件内的的外观以及电学性能进行检查,并根据产品规格标准进行合格与否的判定的工序

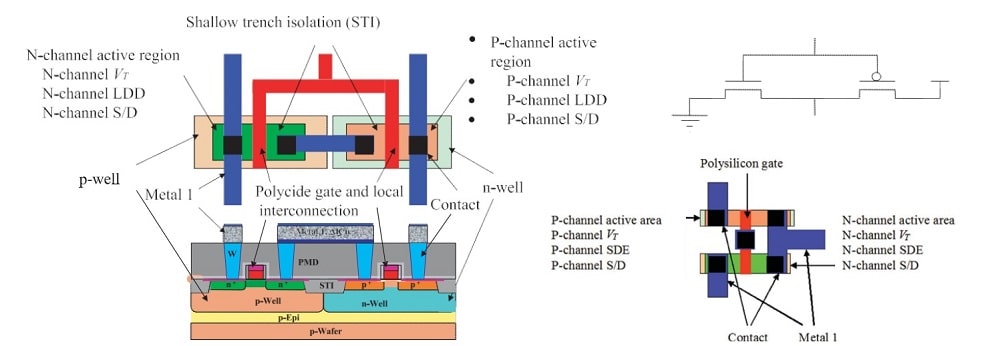

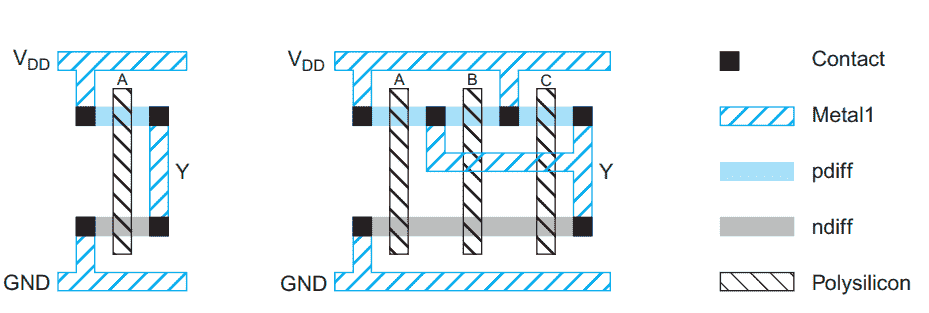

常规平面 CMOS 工艺1只有最底层的器件层(Device layer)包含晶体管,其他层一般只包含金属导线和通孔,用于连接器件层中的不同逻辑块。一般位于上层的金属导线更宽,电阻与部分参数比下层金属更优,常用于模块间连接。当前技术实现多器件层是可以的,但成本较高,下文 3D 硅工艺会做简单介绍。半导体生产工艺可以参考 B 站 CMOS 工艺简介。下图是 CMOS 反相器的硅实现示例,工艺图一般使用不同的颜色代表不同的层与功能

3D 芯片

参考2,芯片中约 40% ~70% 的能量消耗来源于时钟互连网络,而时钟网络通常用很长的全局互连来实现。持续增长的不同信号和技术的集成导致了片上系统 (SoC) 不同的设计概念,这些概念使得目前平面 IC 设计可能不再适用。利用垂直方向的维度,在减轻互连相关的问题的同时使得 SoC 应用变得更加容易。一个对 3D 集成电路3的全面分析显示:在不采用其他电路或设计创新的情况下,只要简单地将一个平面芯片切分成独立的模块,每块占据一个独立的物理层,并用短的垂直层间互连(VILICs)连接起来,性能就会获得显著的提升,且芯片的尺寸也可以得到减小。下图4展示了 3D 芯片的使用与不同类型的实现工艺

3D 芯片很有优势,但成本与一些问题还需要解决,所以当前 3D 芯片还未普及。大多数集成电路中产生的热能量是由晶体管开关导致的。这个热量一般通过硅衬底传导到封装,然后再通过散热片传到周围环境。对于多层器件的设计,上层的器件也会产生大量的热,3D 集成电路,热扩散问题变得更加严峻,它可能导致器件性能的降低,结漏电流提高,芯片的可靠性降低,电迁移失效,以及加速其他失效机制

有几个可能的制造技术可以用于实现多层有源区(单晶硅或再结晶的多晶硅)、相互之间有层间介质(ILD)隔离的3D 电路工艺。例如束再结晶、硅外延生长、晶圆粘接、固相结晶等,细节请参考其他资料

版图设计规则说明了一个制造工艺能可靠密集制造的特征线条所允许的精细程度以及它们相互间允许的接近程度

FET/Fin/GAA/VFET

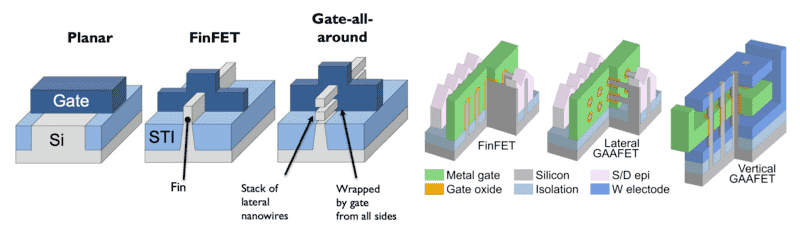

对于传统的 CMOS 工艺(Planar FET),当晶体管的尺寸变得很小时(例如当特征尺寸小于 180 nm),它们就不能完全关断,因而虽然经过每个晶体管的漏电流很小,但当一块芯片上有几百万某至数十亿个晶体管时将会导致非常大的功耗

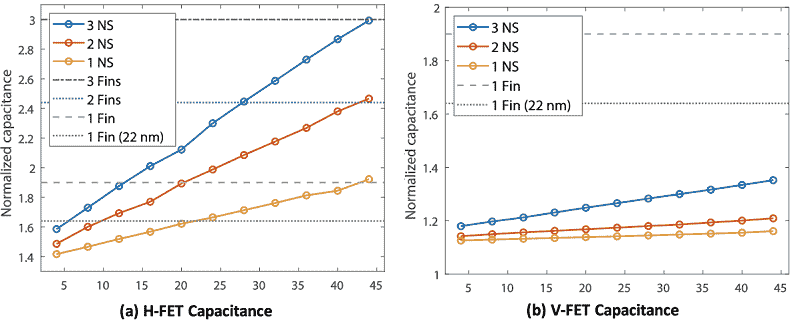

为了减少漏电流并提高晶体管的性能,不同类型的晶体管结构被创造了出来,例如著名的 FinFET。随着芯片制程技术的提升,FinFET 也在不断的进化5,例如 GAA6。GAA(gate-all-around FET)也分水平和垂直两种技术,如下图7。先进 CMOS 工艺可以参考8

版图

λ Rule

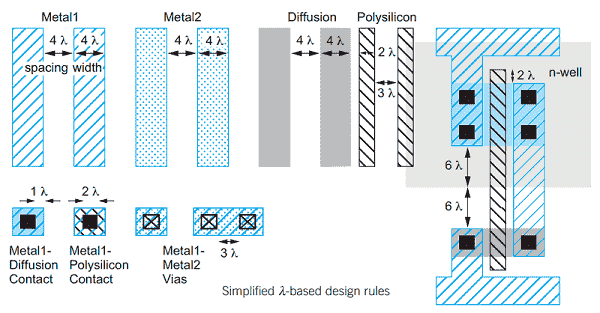

版图设计规则说明了一个具体制造工艺能可靠密集制造的特征线条所允许的精细程度以及它们相互间允许的接近程度

180nm 以下时,设计规则已变得非常复杂并且与具体的工艺有关,这使按比例伸缩的设计规则很难应用。但从简单的一组可伸缩规则中得到的直觉仍然是我们理解较复杂设计规则非常有价值的基础,Mead 和 ConW3y 基于单个参数 λ (λ —般是指所能设计的晶体管最小沟道长度的一半)来表征工艺的分辨率。以下为一个比较保守但易于使用的两层金属 n 阱工艺的版图设计规则

- 金属和扩散的最小宽度和间距为 4λ;多晶硅的宽度为 2λ

- 接触(Contact)为 2λ×2λ,且必须被它的上层或下层包围1λ

- 在需要有晶体管的地方多晶硅应与扩散重叠2λ,在不需要有晶体管的地方多晶硅必须与 扩散相隔 1λ

- 多晶硅和接触与其他多晶硅或接触之间的间距为 3λ;n 阱应包围 PMOS 管 6λ 并与 nMOS 管相距 6λ

上述内容细节请参考9第一章

棒图

由于画版图非常费时,所以设计者在着手画完整的版图前需要有布置单元和预估面积的快速方法。棒图(Stick diagrams)是一种很容易画的图,因为它不需要按比例画

-

Eltes, Felix , et al. “A BaTiO-based electro-optic Pockels modulator monolithically integrated on an advanced silicon photonics platform.” Journal of Lightwave Technology (2019):1-1. ↩︎

-

美 戴维斯 Davis, Jeffrey A, and 美 迈恩 Meindl, James D. 吉规模集成电路互连工艺及设计. 机械工业出版社, 2010. ↩︎

-

Lu, J. Q. , K. Rose , and S. Vitkavage . “3D Integration: Why, What, Who, When?.” future fab int (2007). ↩︎

-

Loo, Roger, et al. “Processing technologies for advanced Ge devices.” ECS Journal of Solid State Science and Technology 6.1 (2016): P14. ↩︎

-

Yakimets, Dmitry, et al. “Vertical GAAFETs for the ultimate CMOS scaling.” IEEE Transactions on Electron Devices 62.5 (2015): 1433-1439. ↩︎

-

Song, Taigon . “Many-tier Vertical GAAFET (V-FET) for Ultra-miniaturized Standard Cell Designs Beyond 5 nm.” IEEE Access PP.99(2020):1-1. ↩︎

-

Radamson, Henry H., et al. “State of the art and future perspectives in advanced CMOS technology.” Nanomaterials 10.8 (2020): 1555. ↩︎

-

Weste, N. H. E. , and D. Harris . “CMOS VLSI Design: A Circuits and Systems Perspective, Third Edition.” Addison Wesley. ↩︎