芯片制造-硅器件

大部分集成电路在硅片上进行生产,一片 9 或者 12 英寸晶圆(Wafer)上可以生产很多相同功能的芯片。每一个从晶圆上切下来的包含逻辑功能的硅颗粒被称为(Die);每个 die 上包含逻辑核心(Core);为了方便封装(Package),die 的边缘一般有一圈 Pads,方便从 Core 引出引脚

MOS

Source&Drain

The terminology of source and drain might initially seem backward. Recall that the current in an nMOS transistor is carried by moving electrons with a negative charge. Therefore, positive current from drain to source corresponds to electrons flowing from their source to their drain

虽然 MOS 晶体管是对称结构,但习惯上我们都说多数载流子从它们的源流向它们的漏。由于电子带负电荷,因此 nMOS 管的源极是源、漏两端口中电平较低的一个。而空穴带正电荷,因此 pMoS 管的源极是这两端中电平较高的一个。在静态 CMOS 门中,晶体管的源极是靠近电源轨线的端口,而漏极是靠近输出的端口

I-V 模型

理想 & 非理想模型

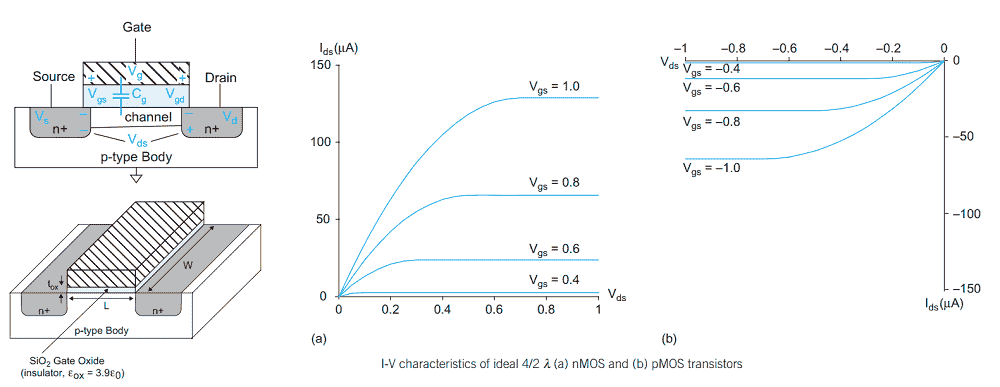

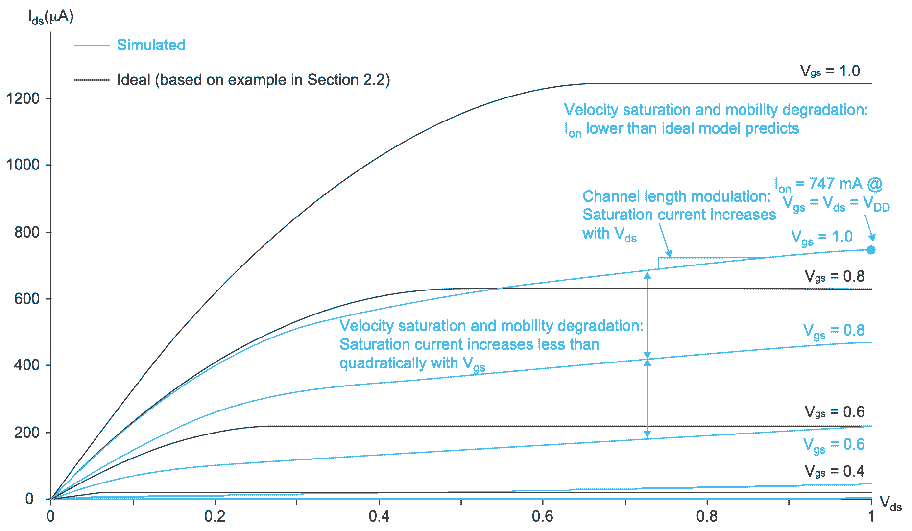

假设沟道足够长,因此横向电场( 源和漏之问的电场)相对较弱,但这一假设对于纳米器件已不再成立。这一模型有多个名称,如长沟道、理想 、一阶或肖克利模型。理想 FET 有三个工作区间:截止、线性和饱和区,线性区源漏电流与源漏电压正相关,饱和区源漏电流与源漏电压无关,理想型 MOS 电流特性如下,饱和电流大小与源漏电压无关:\(I_{d s}=\frac{\beta}{2} V_{G T}^2\)

\[\begin{aligned} I_{d s} & =\frac{Q_{\text {channel }}}{L / v} \\ & =\mu C_{\mathrm{ox}} \frac{W}{L}\left(V_{g s}-V_t-V_{d s} / 2\right) V_{d s} \\ & =\beta\left(V_{G T}-V_{d s} / 2\right) V_{d s} \\ \beta & =\mu C_{\mathrm{ox}} \frac{W}{L} ; V_{G T}=V_{g s}-V_t \end{aligned} \]

随着晶体管体积变小,理想模型已不能精确描述 MOS 的行为。对与纳米器件(100nm~1nm),\(I_{ds}=\frac {\beta} {2} V_{GT}^{\alpha}\),其中 \(\alpha\) 接近 1。其中速度饱和、迁移率退化、沟道调制、阈值电压、璲穿、体效应等效应将影响 MOS 管的行为

构建反型层的最小阈值电压(\(V_{TH}\))并不仅仅与制程相关且不是定值,体效应(\(V_t=V_{t 0}+\gamma\left(\sqrt{\phi_s+V_{s b}}-\sqrt{\phi_s}\right)\))和漏致势垒电压降低(\(V_t=V_{t 0}-\eta V_{d s}\))都会直接影响阈值电压。阈值电压一般随着沟通长度而增大,短沟道 MOS 因为源漏耗尽层更为显著

泄漏

即使当晶体管名义上关断时,它们也会泄漏少量的电流。泄漏机理包括在源和涌之间的亚阀值导电、从栅至体的栅泄漏,以及从源至体和从漏至体的 p-n 结泄漏。对于特征尺寸在 180nm 以上的工艺,除了功耗非常低的应用外,泄漏的影响一般都不大。但在 90nm 和 65nm 工艺中,阙值电压已降得很低,使亚阙值泄漏达到了每晶体管几纳安至儿十纳安的水平,当这个值乘以芯片上几百万至几十亿个晶体管时其影响就很严重

根据量子力学理论,一个原子周围的电子云具有一定的空间分布概率。当栅氧薄至 15~20A 以下时,栅上的一个电子将完全有可能发现自己不正确地处在栅氧的另一侧,也就是它将飞速掠过栅氧到达沟道。载流子这一越过薄绝缘层壁垒的效应称为隧穿(tunneling) ,它将引起穿过栅极的泄漏电流(栅泄漏)

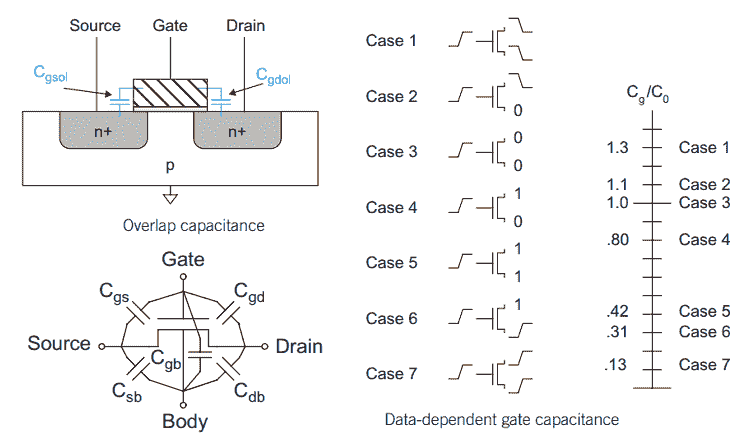

C-V 特性

MOS 管源漏之间的电容包括源漏扩散区和体之间的电容。栅极位于沟道的上方,但它有可能部分覆盖源和漏的扩散区域,因此栅电容由两部分组成:本征电容和覆盖电容。因为覆盖电容的存在,栅极电容大小和晶体管工作状态有关,如上图所示

可以把 MOS 晶体管看成是一个四端器件,它的每一对端口之间都存在电容,其中栅电容包括本征部分(根据工作范围,它可以是与体之间的电容,与源和漏之间的电容,或仅仅是与源之间的电容)及一个与源和漏相覆盖的部分。而源和漏有一个与体之间的寄生扩散电容

延时模型

瞬态 & RC 模型

瞬态响应通过建立 MOS 管的微分方程从而实现延时计算,微分方程采用长沟道模型求解晶体管电流,这对于现代工艺来说是很不精确,这些方程也过于非线性,不能求得闭式解,所以它们必须采用数值方法求解,因而也提供不了有关延时的深刻含义

RC 延时模型采用在逻辑门翻转区间上的平均电阻和电容来近似非线性晶体管的 IV 和 CV 特性。这一近似虽然在详细预测模拟行为方面有明显的局限性,但它却能非常好地估计延时。简化为 RC 模型的电路使用 RC 电路的瞬态响应即可计算出延时

版图效应

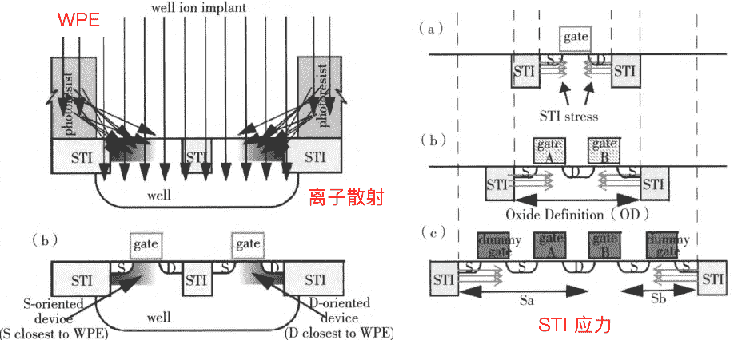

随着半导体工艺缩小到纳米级尺寸,应力对器件的影响越来越显著,这些应力大多和版图布局有关,所以将这些影响称为版图效应。常见的版图效应有浅槽隔离压力效应(Shallow Trench Isolation, STI)、多晶间距效应、边缘效应、阱邻近效应(Well Proximity Effect, WPE)等。器件的特性除了依赖于沟道长度和宽度,还取决于其周围器件及布局。因为周围单元的影响,多晶数量增多,单元性能受多晶数量和间距的影响(多晶间距效应);单元邻近分布,使得中间单元受邻近散射效应和边缘效应的影响,最后导致时序的变化。细节可以参考论文:先进工艺下的版图邻近效应研究进展 / 基于40nm工艺的版图邻近效应研究。BSIM4.5 MOSFET 模型中已经引入了 STI 等参数

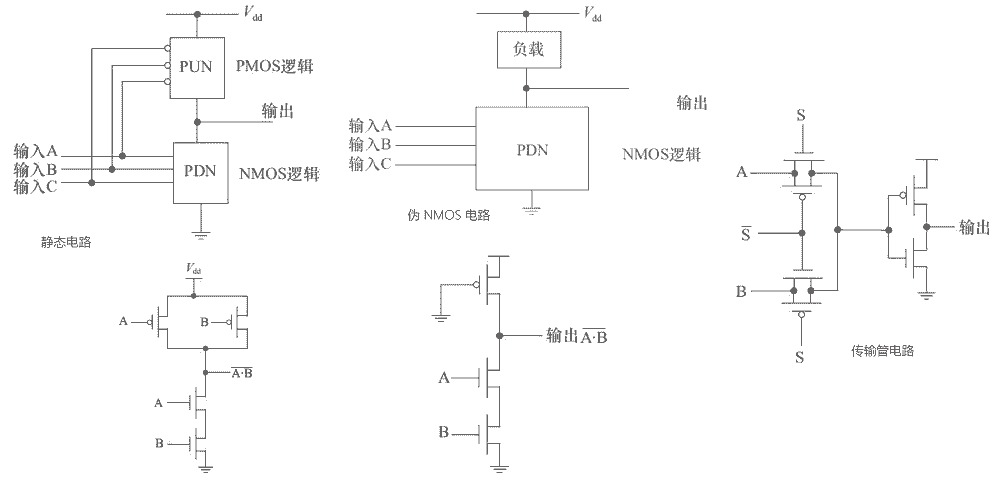

CMOS 电路结构

由于 CMOS 电路中 NMOS/PMOS 管串联个数不能太多,多个晶体管串联会显著降低电路速度,因此在设计中串联个数通常不超过 4。在130nm 工艺条件下,如果设计目标定位在 1GHz,即时钟周期为 1ns,当采用标准单元设计时,触发器时钟至输出延迟约为 0.14ns,触发器的建立时间约为 0.09ns,再去除 0.1ns 的时钟偏斜,最后给组合路径留出的时间为 0.67ns

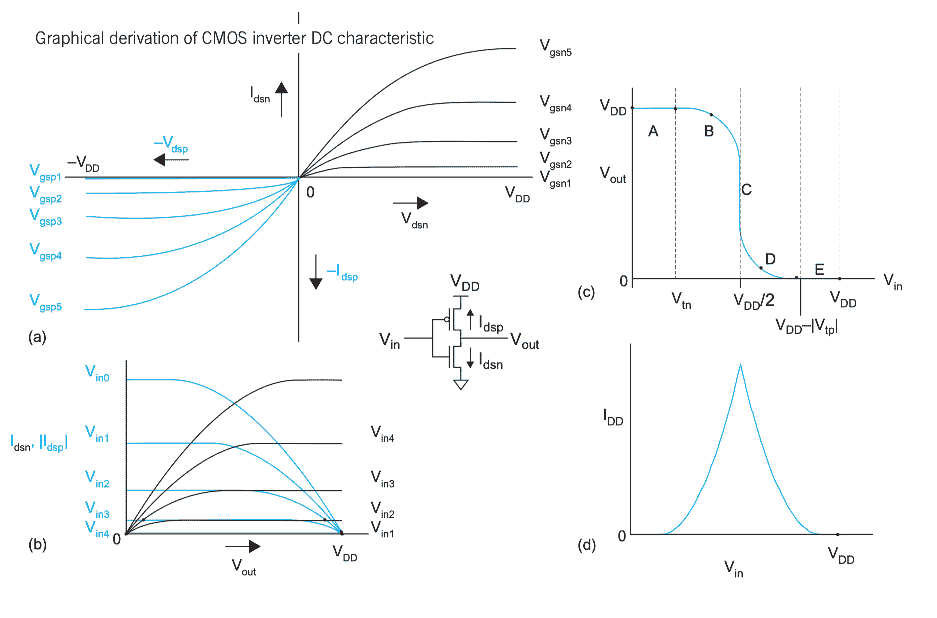

反相器 DC 特性示例

反相器如上图所示,假设 PMOS 和 NMOS 的 \(\beta\) (\(\beta _{n}=\beta _{p}\))值相等,则反相器的阈值电压是 \(\frac {V_{DD}} {2}\) 。因为 PMOS 的空穴载流子比电子慢,顾获得同样 \(\beta\) 值时 PMOS 的沟道要比 NMOS 宽。\(\beta\) 值不同的反相器被称为偏斜反相器

时序单元(Latch&FF)

时序单元的实现有多种方式,其中动态电路的下拉网络(PDN)的构成完全与CMOS一样。这种电路分为两个主要阶段:预充电和求值,处于哪种模式由时钟信号 CLK 决定

在数字电路设计中,设计人员用锁存器 latch 专指电平敏感的时序电路。寄存器(Flip Flop) register 通常由 latch 构成,时钟边沿触发。任何由交叉耦合的门形成的双稳态电路,包括单稳,振荡电路都可称为触发器 flip flop,它是与时钟信号相关的时序电路

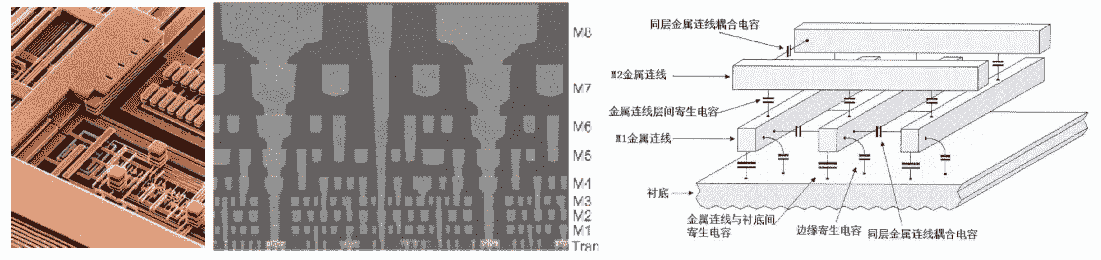

片上导线

一般来说,在具有较多金属层的工艺中,顶层金属线常常较厚、较宽因而具有较低的电阻

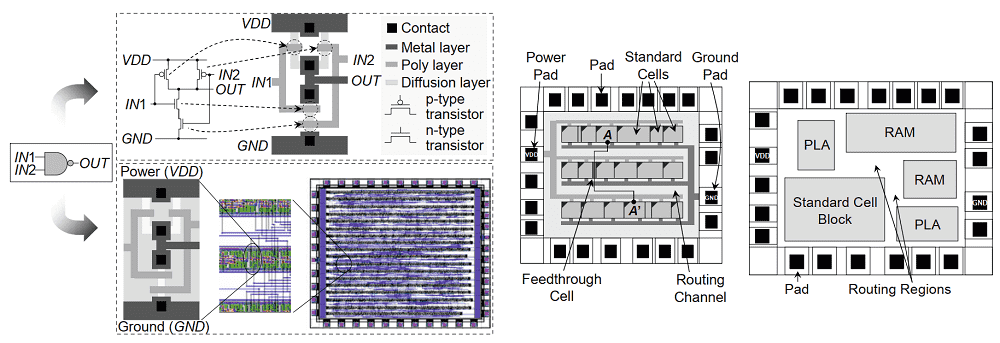

标准单元设计

标准(宏)单元类型有逻辑门单元、驱动单元、时序单元、运算单元、混合逻辑单元(译码器等)、I/O 单元、物理单元(没有逻辑功能,例如 filler )等。不同单元主要关注点不同,例如 IO 单元需要特别关注静电问题

早期基于标准单元的物理实现,由于有限的布线资源,需要专门留有布线通道。现在由于工艺越来越先进,在器件尺寸不断缩小的同时,提供布线资源的金属层数也逐渐增多,单元与单元之间的连接可以直接通过不同层金属进行连接(Over-the-cell,OTC),所以一般情况下,已经不再需要布线通道,且标准单元会跨多个物理层

标准单元设计分为 5 步:需求定义、电路设计实现、电路符号产生、电路功能仿真、电路 Spice 网表输出。设计需要的最基本子单元有 PMOS、NMOS、Vdd 和 Vss,除了这些之外,原理图里还需要输入输出引脚符号和网线(wire),这些基本可以构成大部分的数字电路原理图。一般仿真模型包括五种基本的工艺模型:TT、FF、SS、FS、SF,其中 T 代表 Typical,F 代表 Fast,S 代表 Slow。比如 TT 具体指 NFET-Typical corner&PFET-Typical corner

版图设计

在完成电路设计之后,就进入版图设计阶段。不管数字集成电路设计还是模拟混合集成电路设计,版图设计都是必不可少的重要设计环节。NMOS 晶体管和 PMOS 晶体管是构成 CMOS 集成电路设计的基本器件,其制造需要许多工艺步骤来完成,每一个步骤都包括一系列基本操作。一个基本的 CMOS工艺先从产生有源区开始,晶体管就在这个区域中形成的

版图设计是电路设计精确的物理描述过程,它必须遵守制造工艺、设计流程以及仿真结果(例如:LVS)的—系列约束,它的任务是根据电路功能和性能要求以及工艺条件的限制,设计工艺制造过程中必需的光刻掩模版图。下图是非门、或非门和与非门的版图示例

复杂单元,例如使用传输门(TG)实现的 DFF(D flip-flop),其版图要复杂的多,示例请参考这里

Latch-up & PAE

CMOS 工作方式与 BJT 虽然有一定的区别,但二者基本组成单元均包含 PN 结。不合理的 CMOS 版图结构,会造成属于不同 MOS 的 PN 结形成寄生 BJT,多个 BJT 可能形成正反馈电路从而形成大电流以至损害芯片。这个效应被称为寄生闩锁效应(Latch-up)

根据放大器原理,可以通过不同的方式减少相关效应对芯片的影响。例如使用额外的渗杂区间包围标准单元或者使用绝缘体上硅(SOI,silicon-on-insulator)技术,避免不同 PN 结之间的耦合可以避免闩锁效应

在现代工艺中,等离子刻蚀已被广泛采用,这种方法利用放电产生的游离基与材料发生化学反应形成挥发物,从而实现刻蚀。因此这种工艺会使金属刻蚀过程中收集大量空间静电电荷,当金属积累的静电电荷超过一定数量,形成的电势超过它所接连门栅所能承受的击穿电压时,晶体管就会被击穿,导致器件损坏,这种现象被称为工艺天线效应(process antenna effect),简称 PAE

目前布线工具解决天线效应是采用插入天线二极管和中断金属连线跳换布线层(layer hopping)两种方法实现

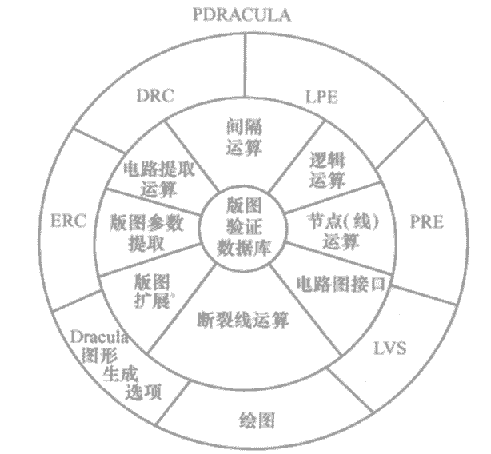

DRC&LVS

设计规则检査(DRC,design rules check)和电路规则检査(LVS,layout versus schematic)是物理验证的两项主要工作。DRC 的主要目的是检査版图中所有因违反设计规则而引起潜在断路、短路或不良效应的物理验证过程,DRC 是保证流片较高良率的统计结果

LVS 与 DRC 同属于物理验证过程,其主要目的是验证版图与电路原理图的电路结构是否一致。首先根据 LVS 提取规则,EDA 工具从版图中抽取出版图所确定的网表文件;然后将抽取出的网表文件与电路网表文件进行比较。抽取的网表为晶体管级的 SPICE 网表,而电路网表为门级的 Verilog 网表,该门级网表需要结合 SPICE 模型/CDL 模型转化为 SPICE 网表,才能与抽取的网表进行逻辑等效性比对

寄生参数提取

电路完成 DRC 和 LVS后还需进行版图寄生电容参数提取(LPE,layout parasitic extraction)和寄生电阻提取(PRE,ptparasitic resistance extraction)。LPE/PRE 完成后我们将会得到一个含有大量寄生元件信息的电路 SPICE 或 CDL 格式网表文件,该网表文件反映了电路版图的精确特性,用它进行 SPICE 后仿真(post-simulation)

RC 提取工具根据电路图结构(或 DEF 文件)就可以建立空间寄生参数的分布,并将结果用标准寄生参数格式(SPF 或 SPEF)文件写出,同时产生晶体管级的网表供后仿真使用

工艺技术文档

电路设计者完成版图后从 EDA 工具导出 GDSII 文件就可以送到代工厂用于掩膜的制作,因此物理后端设计也常被称为从 RTL 到 GDSII 到设计。工艺技术文件(technology file)是晶圆厂提供给设计者用于版图设计的技术文件,其中包含显示信息、互联线工艺和通孔工艺等信息。设计人员在制作版图时需要满足工艺文件中的限制。例如金属最高加工层、方向、最小线宽、最小间距、天线效应、金属电容电阻和最大电流等等

经过版图设计之后形成的标准单元库可以用于后续的物理设计。物理设计所使用的文件种类也很多,例如:

-

电路级(SPICE/CDL 网表),用于器件级仿真或者 LVS 检查

-

符号级(逻辑图),用于逻辑分析

-

版图级(GDSII),用于记录版图完整信息

-

硬件描述语言,Verilog / VHDL

-

物理库 LEF(GDSII 的抽象,便于布局布线),包括互连线的最小间距、宽度、厚度、典型 RC、布线轨道宽度和通孔种类等

- 单元 LEF 文件主要用于定义标准单元、模块单元、I/O 单元和各种特殊单元的物理信息。如对称性、面积大小供布局时使用;它还定义单元输人输出端口的布线层、几何形状、不可布线区域以及工艺天线效应参数供布线用

-

时序库 Liberty(电路综合与时序分析)/ 功耗库 / 噪声库

-

其他

标准单元特点

- 驱动能力:标准单元包括反相器、与门、寄存器、选择器、全加器等多种基本单元,每一个标准单元对应着多个不同尺寸(W/L)、不同驱动能力的单元电路,而且不同驱动强度电路都是基本尺寸或最小尺寸的整倍数;

- 单元高度:所有单元都是等高的矩形,或者髙度是基本高度的整数倍,以确保电路设计阶段不会使用其他非常规的尺寸

- 标准单元与网格的关系:于经典布线器采用基于网格的方法进行布线连接,因此所有单元的输人输出端口的位置、 大小、 形状都尽童满足网格间距的要求

标准单元特征化

针对模块的不同规模和特点,通常有以下五种时序模型:Synopsys 工艺库模型、快速时序模型、接口逻辑模型、抽取时序模型、Stamp 模型。时序模型需要考虑两方面的延迟信息:

- 输入端口到输出端口的延迟信息,称为时序弧

- 输入端口之间存在的时序约束信息,一般指建立/保持时间约束,称为约束弧

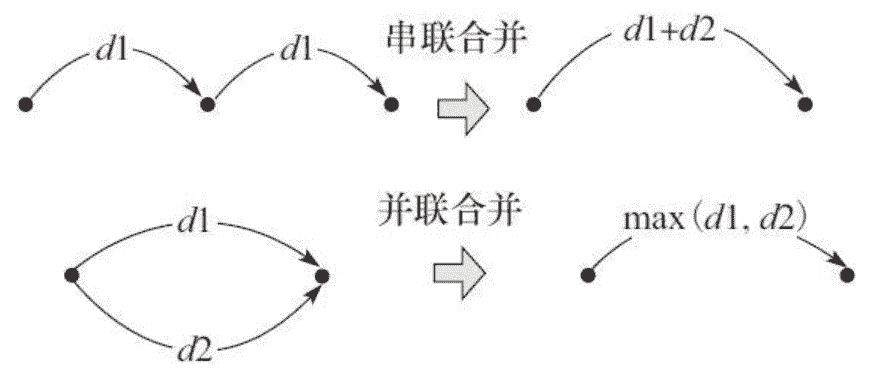

当一个模块规模较大且输入输出端口数较多时,通常需要对其时序弧进行化简,减少延迟弧和约束弧的数量,减少时序建模时工具计算所需的时间以及存储空间。时序信息建模定义了两种基本化简操作:时序弧并联合并/时序弧串联合并

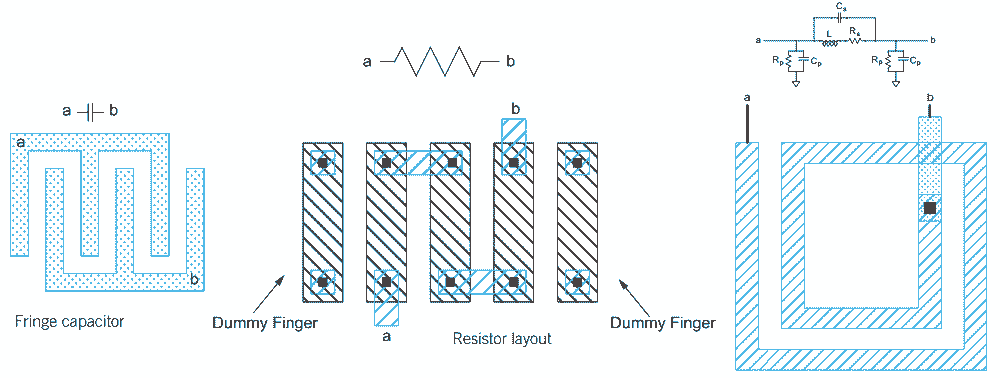

非逻辑单元器件

芯片上还有一些无源器件,例如 CRL / 传输线 / 等;其他器件还有集成光子器件和微电子机械系统(MEMS) ,一个典型的 MEMS 器件就是大家熟知的汽车安全气囊传感器,它是一个由空气桥式电容器构成的小型加速度计,当这个电容器和一些调节电子电路相互集成在一起时可以以用来检测加速度的突然变化。人们也已经制造出像悬臂粱、机械谐振腔甚至微马达等结构

除与或非等逻辑单元,芯片上还有一些特殊用途的标准单元,例如:

- 二极管(diode),反偏二极管可以避免芯片加工过程中的天线效应导致器件栅氧击穿

- 去耦单元,电源和地线之间放置由 MOS 管构成的电容,在瞬态电流增大、电压下降时向电路补充电流以稳定电压

- 时钟缓冲单元 / 延时缓冲单元 / 电压转换单元 / 其他