VLSI 后端设计-简介

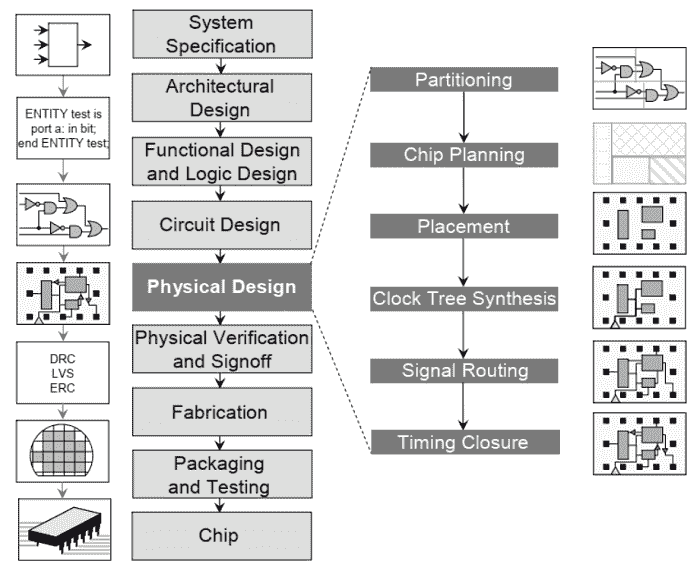

在集成电路设计中,从 Verilog/VHDL 代码(RTL 级)编写验证再通过综合(synthesis)转换成门级网表(gate netlist)的过程称为数字前端设计。接下来的工作就是门级网表的物理实现,即把门级网表转换成版图,这个过程通常称为后端设计(backend design)1

物理设计直接影响电路的性能、面积、可靠性、功率和产量。完整的后端设计由后端半定制与后端全定制两个设计部分组成:

- 后端全定制设计是指在设计初期最先按照设计需求设计出的物理单元库,物理单元库由标准单元库、IP 库及满足特殊需求的定制部件单元等组成。该物理库为后续后端半定制设计提供物理实现基础

- 后端半定制设计是指使用布局布线工具并基于后端全定制阶段完成的标准单元库及 IP 库并根据前端设计完成整个芯片的组装与实现,这个过程又称为数字后端设计(自动布局布线-APR)。常用工具有 IC Compiler、PrimeTime、PrimeRail 等

后端半定制设计由于在设计中占主要部分的标准单元库(standard cell library)里各个单元的高度相等,宽度不限,单元中的电源、地线及输入输出端口位置都有特殊的规定,使得单元与单元连接时变得简单、有条理,布局也有规律,简化了设计过程。当然,使用标准单元进行设计存在一些问题:可用元件件有限、难以高效构造复杂器件(例如乘法器)。后端半定制流程如下:

- 布图规划,决定电路或者模块的形状和布置,以及端口、宏模块的位置

- 电源和地网布线,确定电源(VDD)和地(GND)的位置

- 布局,确定不同模块中所有单元的空间位置

- 时钟综合,确定时钟信号的缓冲、门控和布线,以满足规定的偏移和延迟

- 总体布线,分配布线资源用于连接 / 详细布线、分配布线到指定的金属层

- 时序收敛,优化电路性能

- 物理验证,DRC (Design Rule Checking)、LVS (Layout vs. schematic)、物理电路寄生参数提取等

- 制造 / 封装与测试

半定制流程

目前在物理设计流程中广泛采用两种物理实现方式,一种是展平化设计(Flatten),一种是层次化设计(Hierarchical)

展平式实现方法是大部分芯片的实现方式同时也是层次化设计的基础。在展平化设计中,需要将前端生成的逻辑网表展平,并将设计中的标准单元作为最底层的子节点,不同功能的模块所包含的标准单元都在同一个层次上。层次化设计是在物理设计中保持逻辑设计的层次,并按逻辑关系进行模块划分、设置合理约束,并对布局布线等进行系统级优化。层次化设计对规模不大的设计优化性能并不明显

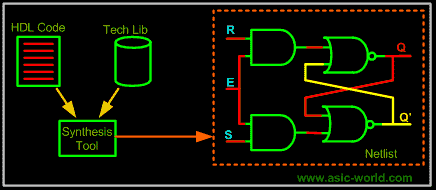

综合(前端流程)

综合(Synthesis)过程将 HDL 转换为门电路,综合是芯片设计的前端流程,也是芯片前端和后端的纽带。 Yosys 是开源的综合工具,Yosys 可以将 HDL 转换为 ASIC 对应的标准单元,或者部分 FPGA 平台下的 LUT 模块。相关示例可以参考 Yosys 官网示例

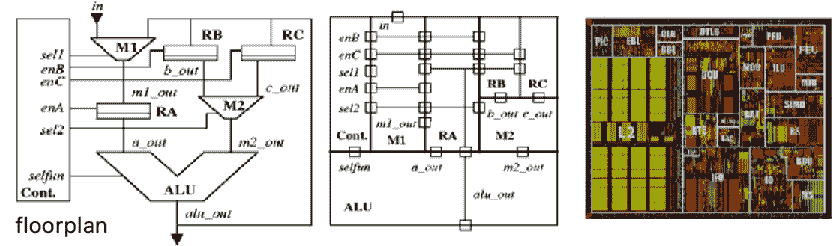

布图规划

布图规划与布局在芯片设计中占据着重要的地位,它的合理与否直接关系到芯片的时序收敛、布线通畅、电源稳定以及良品率

布图规划(FloorPlan)是芯片物理实现中最初的步骤。布局规划主要内容包括对芯片大小的规划、芯片 IO 单元的规划、大量硬宏或模块位置确定等。布局规划包括物理硬 IP 规划、RTL 级模块(Module)规划、I/O PIN 脚规划及电源网络的规划

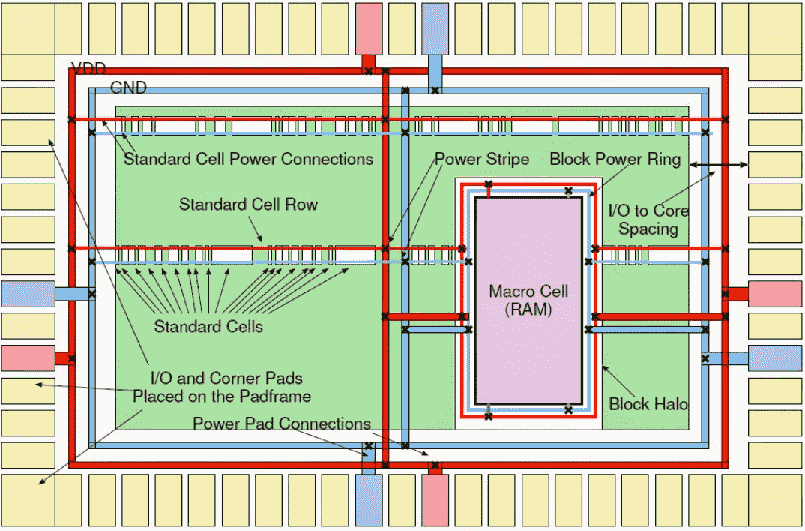

芯片上的供电电压变化较小。因此,在每个工艺阶段随着频率的增加和集成度的提高,芯片内的供电电流都在不断增加。随着工艺的进步,芯片上越来越多金属资源用于供电网和地线网

电源规划

电源规划(Power Plan)是给整个芯片的供电设计出一个均匀的网络,它是芯片物理设计中非常关键的一部分。电源规划在芯片布图规划后或在布图规划过程中交叉完成,它贯穿于整个设计中,需要在芯片设计的不同阶段对电源的供电网络进行分析并根据要求进行修改

通过 Verilog 网表中的定义,我们可以把电源和接地网络(wire)、高低电压网络(supply0、supply1等)、电源和接地(VDD、vdd、VSS、gnd 等)等类型的网络连接到相应的全局电源和接地网络上去。EDA 工具通过一些命令来实现 pin 和电源线等连接,如:

globalNetConnect VDD -type pgpin -pin VDD -inst * -module {}

globalHetConnect VSS -type pgpin -pin VSS -inst * -module {}

电源环线(power ring)是指为了均匀供电,包围在标准单元周围的环形供电金属,它也是连接供电 I/O 单元和标准单元的桥梁;电源网格是为了平均分布电流,缩短电流回路,在有效减小电压降的同时,避免由于电流分布不均时造成的热点(hot spot)现象以及电迁移问题。电源条线所选用的电源层也根据 LEF 中的规定所选,纵向必须用偶数层走线,横向必须用奇数层走线。 由于髙层金属具有较小的寄生电阻,用高层金属走线可以有效地减少电压降

布通性

当读人设计数据和用户定义芯片的面积之后,EDA 工具根据 LEF(或其他工艺文件)工艺内容中布线间距(Pitch)的大小,在整个芯片内部自动生成各金属层连续、规则的布线轨道布线轨道是指芯片内部专门用于布线的路径,布线通道是每两条或多条布线轨道的空间,它们的上面是不可以摆放标准单元的。在模块四周通常还预留不允许摆放标准单元仅供专门布线的晕道(halo)。标准单元占据了底层金属的绝大多数布线轨道,当芯片局部出现拥塞时,采用布线晕道的定义会增添更多底层的布线通道

当两个子模块在芯片内部的空间跨度比较大时, 有时还需要定义直通(feedthrough)布线通道,从而满足时序和布线的要求

Flip-Chip

无论是设计还是放置,输人输出接口单元的内容都是比较复杂的。I/O 单元的类型有:数字输人/输出单元、数字双向输入输出单元、静电保护单元、给 I/O 接口单元供电的单元、给芯核供电的单元、数字填充单元、模拟供电单元、模拟输入单元、模拟输出单元、模拟填充单元等等。IO 单元的分配要综合考虑印制板走线、封装形式、供电情况以及内部模块结构,从而保证信号从芯片内部传递到外部时其路径最短,同时要求从 I/O 单元关键引线到封装点时,避免信号交叉,方便封装基板的制作,减少基板上的走线层数

当芯片面积较大(如大于 \(1cm \times 1cm\))、芯片时序较为紧张时,则采用倒置封装(flip-chip)设计,即 I/O 单元的分布不是四边摆放, 而是均匀分布在芯片的内部

布局

布局又称标准单元放置,它实际上包括对 IO 单元的排序放置、大模块(block)放置和标准单元放置的规划。在芯片的布图规划阶段完成了芯片的整体规划,在布局阶段则是其细节的实施

大规模集成电路的布局(Placement)技术包括全局布局、详细布局和合法化。全局布局给标准单元和大型电路模块( 例如宏块) 分配了位置。 但是,这些位置一般不会与电源线连接,这些位置可能有连续的坐标( 实数的) 而不是离散的坐标

模块大小的确定主要看面积利用率的大小,它是指标准单元总面积与模块在芯片内部所分布面积之比。当初始利用率低于 70% 时,较容易布通,而当利用率高于 85% 时,则会出现较大的拥塞,从而导致无法完成布线

芯片的物理设计需要在不同阶段对芯片需要实现的目标进行评估,从而尽早发现问题。在布局完成后需要评估的目标主要有:拥塞(congestion)程度的评估、延迟和时序预估、供电预估

步骤上布局可以分成三个阶段:结群布局(clustering)、全局布局(global placement)、详细布局(detail placement),每个阶段都有其相应的算法。常见的布局优化目标有基于布线拥塞的优化、基于时序的布局优化和基于噪声的布局优化等等

扫描链重组

扫描链(scan chain)是可测试性设计(DFT)的重要内容,它将芯片中所应用的普通寄存器替换成带扫描功能的多输人输出扫描寄存器,首尾连接成串,从而实现附加的测试功能。扫描链在综合阶段通过专门的 DFT 工具产生,在物理设计阶段,我们需要定义扫描链,EDA 工具则根据读入的时序库自动地识别扫描单元

大规模集成电路的扫描链条数达几十条以上,对扫描链进行重组能有效地节约布线空间。当然,对于利用率不高的 I/O 限制型设计,由于布线通道比较充裕,设计者也可以跳过重组扫描链

合法化与详细布局

合法化一般假设元胞在版图区域中分布的相当好,而且相互重叠相当小。一旦得到一个合法布局, 它可以在给定目标下,采用详细布局技术对布局进行改善,如通过交换相邻元胞来减少总线长或是当没有可使用的空间存在时, 移动元胞到行的另一端

时钟树综合

CTS 的目的在于让时钟信号均匀的到达所有时序器件,并尽量减小时钟偏移(skew)和延迟(latency)

时钟信号通常在整个芯片中有最大扇出、通过最长距离、以最高速度运行的信号。时钟信号必须保证在最差的条件下,关键的时序要求能得到满足,因此对时钟信号任何不当的控制都可能导致芯片功能紊乱,可能会将错误数据锁存到触发器导致功能性的错误

门控时钟

芯片工作时,很大一部分动态功耗是由时钟网络的时钟信号翻转消耗的。为了减少时钟网络的功耗消耗,引入门控时钟的方法对时钟网络翻转功耗的抑制作用最强。门控时钟是指一个时钟信号与另外一个非时钟信号通过逻辑转换后再输出的时钟。通过一个逻辑信号来控制时钟信号的起作用时间,这样可以关闭芯片上暂时用不到的功能模块的时钟,从而实现节省功耗消耗的目的

布线

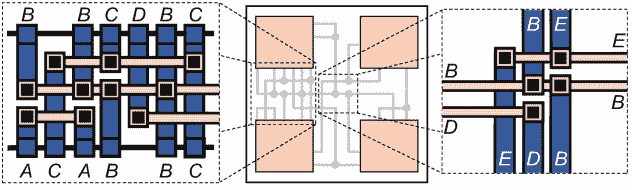

布线(Route)通过金属层连接布局、CTS 后的标准单元、宏模块和片上焊盘(Pads)。如上图所示,不同层的导线使用不同的颜色表示。上图截取自 FPGA 布局示例

进入深亚微米设计后,因为随着器件尺寸的不断减少和电路规模的扩大,门延时越来越小,限制电路性能提高的主要因素变成了互连延迟。在超大规模集成电路中,互连线所引起的时延已占整个芯片时延的 70% 以上

布线(Route)是继布局和时钟树综合之后的重要物理实现过程,其内容是将分布在芯片核内的模块、标准单元和输入输出接口单元按逻辑关系进行互连。其要求是完成逻辑信号的互连,并在满足各种约束条件下进行优化

布线与布线格点

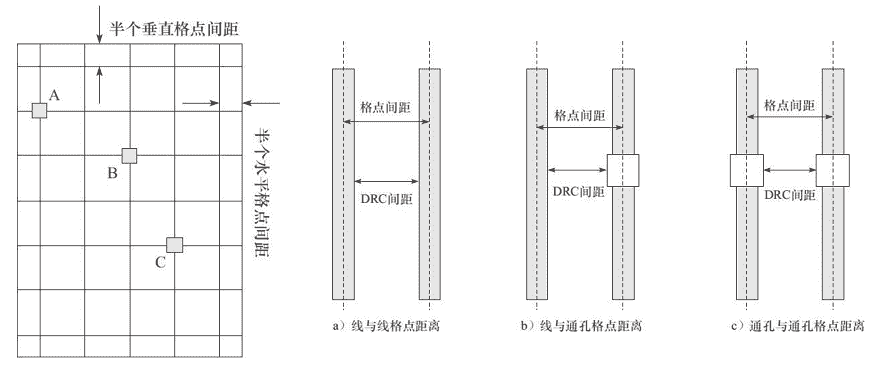

布线格点指的是布局布线中走线规则下垂直水平方向上的交叉节点,格点间距可以根据 3 种形式来设置,即线与线距离、线与通孔距离、通孔与通孔距离。垂直水平布线规则定义了金属层走线方向、走线金属宽度,走线金属间距和走线通道偏移值

标准单元端口分为信号端口和电源端口两类,基于标准单元自身版图的特殊要求,需要对这两类端口进行不同的设置。标准单元的信号端口即输入输出 PIN 脚,输入输出 PIN 脚应该在垂直与水平布线通道的交界处,即格点处

在标准单元库中,所有单元都是同一高度的。单元版图允许背靠背的连接来分享电源和地线,所以标准单元的电源端口 Vss 和 Vdd 在单元拼接时,由于单元背靠背或者相邻连接就自动拼接在一起了

下图所示的金属层 3 和金属层 5 用于水平走线、金属层 4 用于垂直走线,通过单元端口的错开放置有效提高了布线通道利用率。标准单元的 Vdd 与 Vss 金属线通过上下两个方位的单元进行无缝拼接。标准单元拼接时阵列间没有间隔,这使面积减少到最小,但是对于阻塞比较严重的设计,不得不在标准单元行之间设置间距来增加足够的布线通道

由于电子的载流子迁移率大于空穴的载流子迁移率(一般是两倍多),所以 P 管宽度一般比 N 管大,而或非门是 N 管并联,P 管串联。为了满足实际需求,可以根据逻辑功能设计不同尺寸、不同驱动能力的单元。一般的逻辑单元都设计了至少四种不同驱动能力的单元用来满足不同的设计需要

时序分析

静态时序分析(STA,Static Timing Analysis)是验证片上逻辑有效性的一种方式,常见的开源工具有 OpenTimer、OpenSTA 等

ECO

ECO 是 Engineering Change Order 的简称,泛指项目开发过程中的改动。布局布线设计流程中的 ECO 指的是设计后期在保持原设计布局布线结果基本不变的基础上作的小规模改动和优化的过程