STA-基本概念

STA 应用于芯片设计的各个环节,例如综合(Synthesis1)、布局(Place)等。老的芯片生产工艺对噪声与耦合(Noise and Coupling)不太敏感,但深亚微米(小于0.25μm)和纳米(小于0.1μm)技术中这些现象是影响延迟(Delay)和功耗(Power dissipation)的重要因素

时序分析(Timing Analysis)包含静态时序分析(Static Timing Analysis, STA)和时序仿真(Timing simulation),前者在分析的时候不关注输入端的实时信号。STA 和时序仿真各有其特点:

- 使用时序仿真分析千万级门电路设计非常耗时甚至无法分析,STA 可以做完整的电路分析和检测

- STA 可以做其他技术很难做的串扰、噪声和 PVT 分析

- 当然 STA 也有缺点,例如 STA 无法分析 Reset sequence、X-handling 等。静态时序分析所计算的路径延时是最坏情况下的延时,由此获得的最高时钟频率通常太保守,所留的设计余量过大,会增加功耗和成本

STA 主要关注互联线(Interconnect)、时钟(Clocks) 和耦合(Coupling),在不同的分析阶段为减少复杂度,会简化分析过程。例如在逻辑分析阶段使用 Ideal interconnect(忽略寄生 RCs,传输延迟也默认为 0)、Ideal coupling 和 Ideal clock(zero delay);Global Routes 阶段使用 Wireload model(RC based on the fanouts of a cell);Final Routes 阶段使用更精确的 RCs 、考虑串扰(Crosstalk noise)和 Propagated clock(real delays)

Synopsys 和 Cadence 等 EDA 公司都有自己的 STA 工具,比如 Synopsys 的 PrimeTime (PT):

The PrimeTime Suite performs full-chip, gate-level static timing analysis, which is an essential part of the design and analysis flow for chip designs. The tool exhaustively validates the timing performance of a design by checking all paths for timing violations, without using logic simulation or test vectors

PT 执行时序分析时需要各种不同类型的文件,比较常见的有 .lef、.def、.lib 和 .sdc 等

常见缩写

| 缩写 | 全称 | 备注 |

|---|---|---|

| TNV | Total Number of Violations | |

| SPEF | Standard Parasitic Exchange Format | IEEE Standard |

| GBA | Graph based analysis | |

| PBA | Path Based Analysis | |

| POCV | Parametric On Chip Variation analysis | |

| AWP | Advanced Waveform Propagation | |

| CCS | Composite Current Source model for delay and noise | Liberfy Standard |

| QTM | Quick Timing Model | |

| ETM | Extracted Timing Model | |

| DMSA | Distributed Multi Scenario Analysis | |

| SI | Signal Integrity | |

| DVFS | Dynamic Voltage and Frequency Scaling | |

| ECO | Engineering Change Order |

时序路径

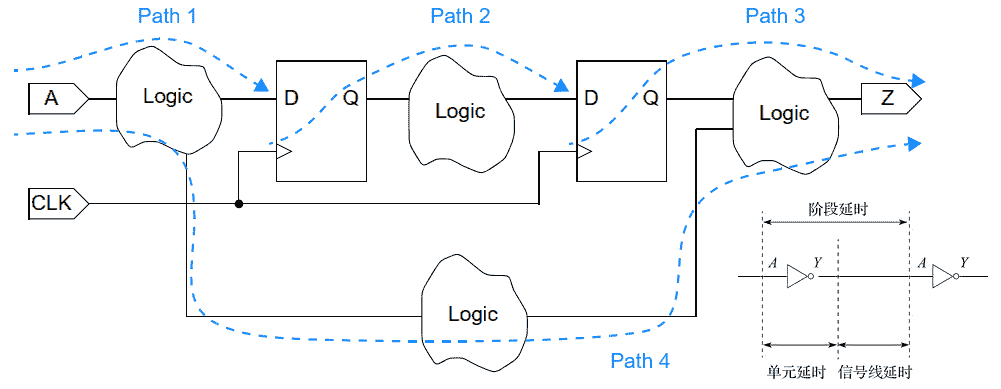

PrimeTime 对电路进行分析时会将逻辑电路分解为时序路径(timing path)。时序路径是数据信号传播过程中所经过的逻辑路径

每一条时序路径都有起点(startpoint)和终点(endpoint)。新数据在时序路径起点由时钟边沿触发,通过时序路径中组合逻辑电路(combinational logic)部件,下一个时钟边沿将触发当前时序路径终点的时序部件,以捕获由组合逻辑部分处理后的数据

\[\begin{array}{lll} \hline \text { Path } & \text { Startpoint } & \text { Endpoint } \\ \hline \text { Path 1 } & \text { Input port } & \text { Data input of sequential element } \\ \text { Path 2 } & \text { Clock pin of a sequential element } & \text { Data input of a sequential element } \\ \text { Path 3 } & \text { Clock pin of a sequential element } & \text { Output port } \\ \text { Path 4 } & \text { Input port } & \text { Output port } \\ \hline \end{array} \]

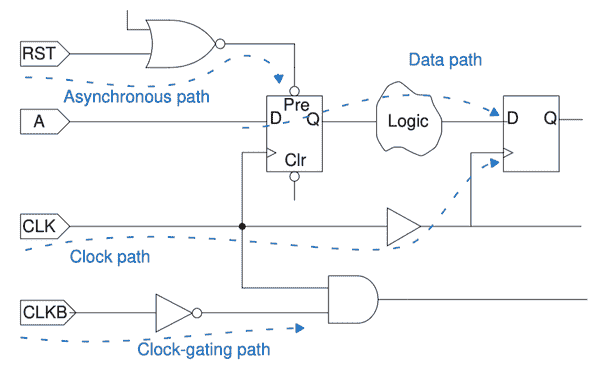

如上表,因为时序路径的起点和终点各有两种,所以时序路径的类型有四种:触发器/触发器、触发器/输出、输入/触发器、输出/输出。按照功能,时序路径可以分为数据(Data path)、异步(Asynchronous path)、时钟(Clock path)和时钟门禁(Clock-gating path)等几种类型,如下图所示

组合逻辑电路常包含多条路径,PT 使用最长路径(longest path)计算最大延迟(Max Delay),使用最短路径计算最小延迟。将设计分解为时序路径后,PT 开始计算每条路径的延迟,路径上的延迟包含两类型:单元延迟(Cell Delay)和网络延迟(Net Delay,或称为信号线延迟)。Cell 一般就是基础的单元电路,例如与或非门和寄存器等;Net 用于连接单元电路或者模块,Net 一般有一个驱动端(特殊设计一个 Net 也可能有多个驱动端)和多个负载,布线后,Net 可能会跨多个金属层,不同的金属层有不同的电阻和电容系数

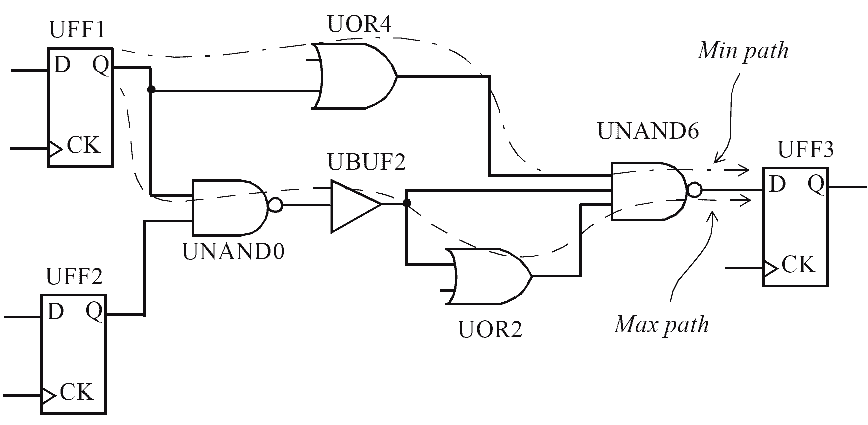

Max/Min 路径

信号由前置时序部件传递到下一个时序部件会经由组合逻辑模块,组合逻辑因设计的需要必然有长短不一的路径(信号通过的基本单元数不同),从而造成到达下一级时序单元的信号有快有慢(最大/Max、最小/Min)。大部分 STA 工具只考虑这组路径中最快和最慢的两个

时序例外

时序例外( Timing Exceptions),一些特殊的时序路径需要通过命令进行设置,例如不需要检查时序的路径(False path)、多时钟周期路径(Multicycle path)和限时路径(Minimum or maximum delay path)等

路径族

STA 中时序路径需要有有效的起点(输入端口或者时序部件的时钟端)和终点(输出端口或者时序组件的数据输入端)。同一个路径族(Path Group)其路径终点有相同的时钟信号。所有异步模块有一个默认的路径族。参考 PT UG,path group 的来源主要是下面三个:

-

相同 Capture Clock 的路径归属于 Capture Clock 同名的 Path Group

-

PT 默认定义的 Group,例如

**async_default** / **clock_gating_default** / **default** / none- default Group 保存由

set_max_delay / set_min_delay等类似 SDC 约束的 Path - async default 保存 recovery/removal 相关约束

- clock gating default,保存 clock gating setup/hold 相关约束

- default Group 保存由

-

用户通过

group_path命令定义的 Group

时序图

静态时序分析中,数字逻辑电路首先转换成时序图(timing graph)的形式,再基于时序图来计算路径延迟的总和,如果所有的路径都满足时序约束和规范,那么就认为设计满足时序约束规范

时序弧

STA 是基于时序弧(Timing Arcs)数据的时序分析。时序弧是用来描述两个节点延时信息的数据,单元延时中的时序弧分为基本时序弧和约束时序弧两类,其中约束时序弧用来表示输入端口之间存在的时序约束信息。基本时序弧包括组合时序弧(combinational arc)、边沿时序弧(edge arc)、复位清零时序弧(preset and clear arc)、三态使能时序弧(three state enable and disable arc)等。约束时序弧包括建立时序弧(setup arc)、保持时序弧(hold arc)、恢复时序弧(recovery arc)、移除时序弧(removal arc)和脉宽时序弧(width arc)等

时序弧的约束信息可以参考刘峰《静态时序分析》第 2.6 节 和 OpenSTA 中提供的示例 liberty 文件。一个 PIN 可能对应多个时序弧约束

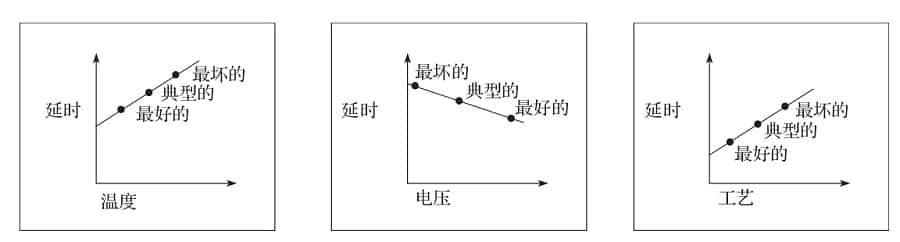

PVT

为了使静态时序分析的结果更接近实际芯片工作环境的情况,需要对芯片设计工作环境,包括工艺、工作电压、工作温度等参数进行设置,该参数的组合简称为 PVT(Process、Voltage、Temperature)

对鲁棒性要求非常高的设计,需要在不同的边界条件(Corner Case,或者称之为极端情况)下测试设计时序的正确性

- WCS (Worst-Case Slow): 慢工艺(Process is slow)、高温(125C)、低压(\(1.2V \times 0.9\))

- TYP (Typical): 典型工艺、温度(25C)和电压(1.2V)

- BCF (Best-Case Fast): 快工艺(Process is fast)、低温(-40C)、高压(\(1.2V\times1.1\))

Single/BC_WC/OCV

细节可以参考 《集成电路静态时序分析与建模》 / Primetime set_operating_conditions 命令介绍 /

分析时序信息时需要考虑 PVT 对时序的影响,故 STA 支持不同类型的 PVT 组合。单⼀分析模式(Single)只会在指定的⼀种⼯作条件下检查建⽴时间和保持时间;最好-最坏(BC_WC,best case worst case)分析模式,静态时序分析⼯具会在 PVT 环境中的最好(BCF)的和最坏(WCS)的⼯作环境下分别检查保持时间和建立时间;因为同芯片上不同位置温度不同,故 BCWC 分析无法捕获最极端的情形。相比于 BCWC,OCV 在分析数据路径和时钟路径时会使用不同的 liberty,以模拟最极端的时序场景

Setup analysis is done using slowest launch and fastest capture, Hold analysis is done using fastest launch and slowest capture

If you provide library data for two corners, OCV will use both, increasing the difference between launch and capture path delays, causing failures that would never occur in real life on a single chip, so, with OCV, you should provide library data fot only one corner

因为 OCV 模式太过悲观,故提出了 CRPR、AOCV 和 POCV(SOCV)(\(Dly=Dly_{nom} + Dly_{var}\times P\))等技术。使用 POCV 需要 liberty 中包含 LVT(liberty variation format)表格

AOCV 利用 path 长度估算这条 path 上所有 cell/net 的 derate 值,cell/net 长度根据对角线规则计算。根据统计规律,路径越长,derate 值越接近 1.0

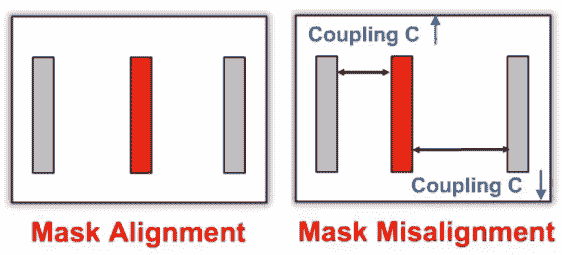

RC 角

在双重曝光(Double Patterning)场景下,因为掩膜精度和曝光对齐过程中的误差,金属层上相邻导线的距离会有偏差,因此造成了耦合电容的变化。如上图所示,没对齐的曝光,会造成左侧两线耦合电容增加,右侧两条导线耦合电容减小。参考下表,影响导线电容电阻的因素有温度、宽度、高度等,因为芯片制造的精度问题,需要考虑 RC 的 OCV

\[\begin{array}{|l|l|l|l|} \hline \text { Parameters } & \text { Resistance } & \text { Surface Caps } & \text { Coupling Caps } \\ \hline \text { Temperature } \uparrow & \uparrow & & \\ \hline \text { Width } \downarrow & \uparrow & \downarrow & \\ \hline \text { Thickness } \downarrow & \uparrow & & \downarrow \\ \hline \text { Space } \downarrow & \text { No Effect } & \text { No Effect } & \uparrow \\ \hline \end{array} \]

不同 RC Corner 的概念如下

K-factors

CMOS 通用延时计算模型将时序路径的延时分成 4 个部分,总延时是这 4 部分延时之和:\(D_{\text {total }}=D_{I}+D_{S}+D_{C}+D_{T}\)

在实际时序分析中,时序分析工具在计算总延迟时,还需要考虑工艺、温度和电压变化的情况,因此部分参数要乘以比例系数

\[D_{\text {scaled }}=D \times\left(1+\Delta_{\text {process }} \times K_{\text {process }}\right) \times\left(1+\Delta_{\text {temp }} \times K_{\text {temp }}\right) \times\left(1+\Delta_{\text {voltage }} \times K_{\text {voltage }}\right) \]

部分比例因子定义示例如下:

/* k-factors */

k_process_rise_transition

k_temp_rise_transition

k_volt_setup_rise

...

时序约束

常见的时序检查有:setup/hold, recovery/removal, data-to-data, clock-gating setup and hold, the minimum pulse width for clock signals, Propagation Delay

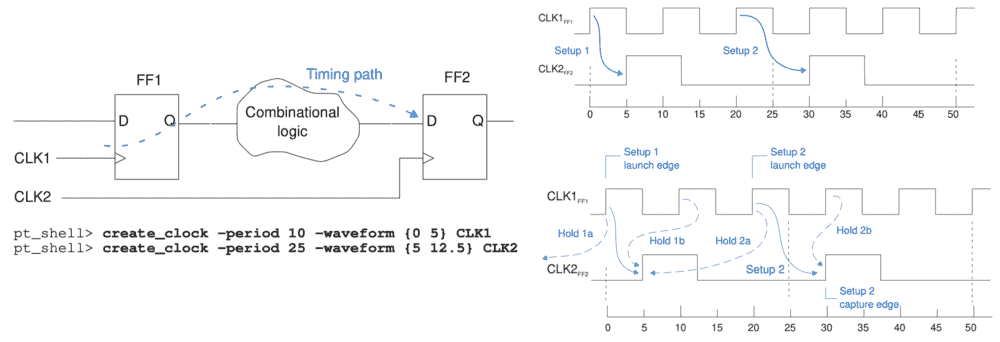

时钟沿规则

PrimeTime looks at the relationship between the active clock edges over a full repeating cycle, equal to the least common multiple of the two clock periods. For each capture (latch) edge at the destination flip-flop, PrimeTime assumes that the corresponding launch edge is the nearest source clock edge occurring before the capture edge2

The hold relationships checked by PrimeTime are based on the clock edges adjacent to those used to determine the setup relationships. To determine the most restrictive hold relationship, PrimeTime considers all valid setup relationships. For each setup relationship, PrimeTime performs two different hold checks:

- The data launched by the setup launch edge must not be captured by the previous capture edge

- The data launched by the next launch edge must not be captured by the setup capture edge

如上图,参考2,PT 会考虑从时刻 0 开始的两个最小公倍数周期来确定时序路径的触发沿(Launch)和捕获沿(Capture)。对于同一个时钟,时刻 0 前没有额外的信息,所以捕获沿是第二个周期的上升沿(假设 Cell 为上升沿触发)

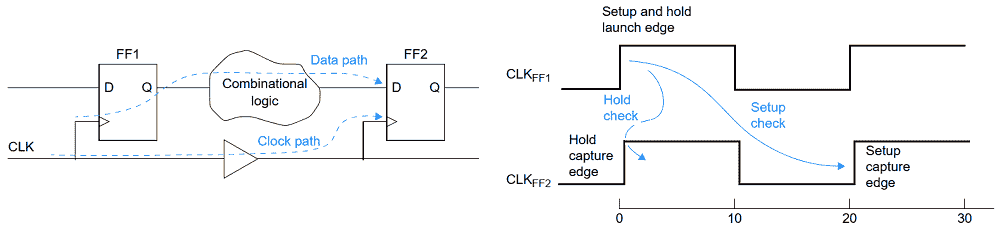

建立/保持

默认情况下 STA 工具假设信号在一个时钟周期内通过时序路径,因此 STA 进行 Setup check(建立时间检查)时验证一个时钟周期内,数据是否可以从 FF1 传输到 FF2 并被 FF2 有效捕获。因为寄存器的物理特性,寄存器 FF2 有效捕获数据,需要所有信号到达 FF2 D 端的时间比时钟沿早一些,所以 STA 此时考虑组合逻辑电路中最大时序路径进行 setup check

寄存器在捕获数据时,需要输入数据在时钟沿附近保持一段时间(setup check 需要数据在时钟沿前一段时间保持稳定,hold check 需要数据在时钟沿后一段时间保持稳定),hold check(保持时间检查)用于检查前置最短时序路径是否满足这样要求

可以使用极限法来考虑 hold check。假设 FF1 在 CLK 上升沿时瞬间就将新的信号传递到了 FF2 的输入端,且假设 FF2 的 CLK 有延迟,那么 FF2 与 FF1 在同一个时钟边沿获得了新的信号,这与事实相悖,所以同一个时钟周期内 FF1 的输出一定要在 FF2 时钟上升沿之后的某个时段到达 FF2 的输入,此时 FF2 的时钟已经失效,故不会在被 FF1 的输出影响

恢复/移除

恢复/移除(Recovery/Removal)主要检查寄存器复位端信号和时钟信号之间的时序约束。如上图所示,寄存器 UFF6 复位,将 CDN 端设置为 0 即可,不需要考虑 CDN 信号和时钟信号之间的关系。UFF6 恢复正常捕获功能时(UFF6/CDN 为 1),UFF6/Q 应该依旧是复位状态(至少是稳定的),后续时钟,UFF6 才应该捕获数据。UFF6/CDN 从 0 跳变为 1 的信号沿前后如果有时钟沿,那么 UFF6/Q 的状态不稳定(可能是复位状态,也可能是 UFF6/D 的值)。故需要检查 UFF6 恢复正常数据捕获前后 CDN 和 CK 信号之间的关系

STA vs DTA

在 16nm 工艺条件以下的 SoC 设计以及物联网(IoT)超低电压设计中,以工艺角时延为基础的 STA 计算已经不再准确,而需要采用基于晶体管级模拟的动态时序分析方法(Dynamic Timing Analysis,DTA)。细节可以参考论文3